# Product Document

### **Datasheet**

DS000693

# TMF8820/21/28

# **Multizone Time-of-Flight Sensor**

v5-00 • 2022-Apr-14

## **Abstract**

The TMF8820/21/28 is a dToF (direct time of flight) wide field of view optical distance sensor module achieving up to 5000 mm target detection distance and has up to 3x3, 4x4, 3x6 or 8x8 zones.

# **Content Guide**

| 1                                      | General Description 3                                                                                                                |

|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| 1.1<br>1.2<br>1.3                      | Key Benefits & Features3Applications5Block Diagram5                                                                                  |

| 2                                      | Ordering Information 6                                                                                                               |

| 3                                      | Pin Assignment7                                                                                                                      |

| 3.1<br>3.2                             | Pin Diagram7 Pin Description8                                                                                                        |

| 4                                      | Absolute Maximum Ratings 9                                                                                                           |

| 5                                      | Electrical Characteristics 10                                                                                                        |

| 6                                      | Typical Operating Characteristics13                                                                                                  |

| 6.1                                    | 4x4 Zones Operating Mode (only TMF8821                                                                                               |

| 6.2                                    | and TMF8828)15 8x8 Zones Operating Mode (only TMF8828)16                                                                             |

| 7                                      | Functional Description 17                                                                                                            |

| 7.1<br>7.2<br>7.3<br>7.4<br>7.5<br>7.6 | General Operating Description17Timing Diagrams18Calibration19Algorithm Performance21Typical Optical Characteristics33I²C Interface35 |

| 8                                      | Register Description 38                                                                                                              |

| 8.1<br>8.2                             | Register Overview                                                                                                                    |

| 8.3                                    | appid=0x03, any cid_rid - Main Application Registers46                                                                               |

| 8.4                                    | appid=0x03, cid_rid=0x10 - Measurement Results 56                                                                                    |

| 8.5                             | appid=0x03, cid_rid=0x16 - Configuration Page                        |                |

|---------------------------------|----------------------------------------------------------------------|----------------|

| 8.6                             | appid=0x03, cid_rid=0x17/0x18 - User Defined SPAD Configuration      |                |

| 8.7                             | appid=0x03, cid_rid=0x19 - Factory Calibration                       |                |

| 8.8                             | appid=0x03, cid_rid=0x81 – Raw Data Histograms                       |                |

| 8.9                             | appid=0x80 – Bootloader Registers                                    |                |

| 9                               | Application Information                                              | 87             |

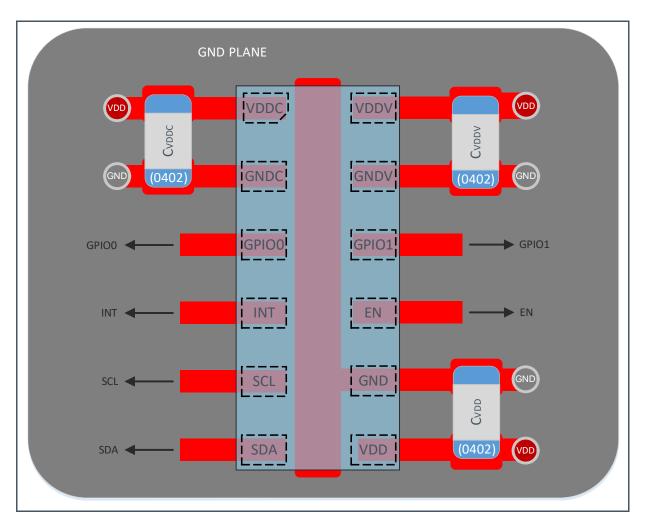

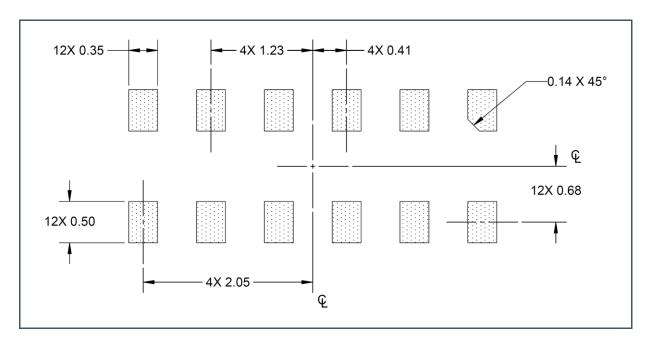

| 9.1<br>9.2<br>9.3<br>9.4<br>9.5 | SchematicPCB LayoutExternal ComponentsPCB Pad LayoutSoftware Drivers | 89<br>90<br>90 |

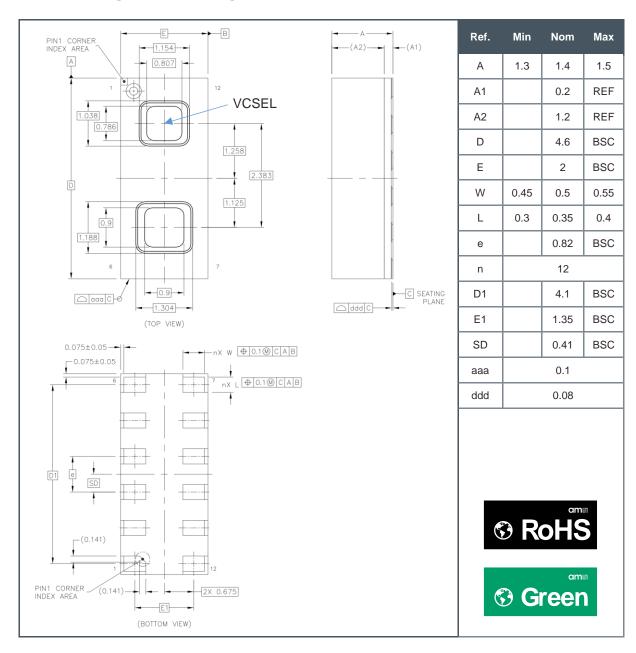

| 10                              | Package Drawings & Markings                                          | 92             |

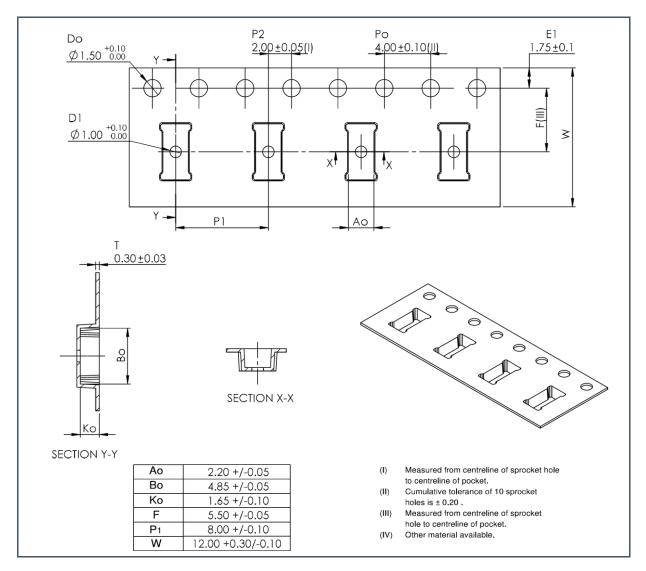

| 11                              | Tape & Reel Information                                              | 93             |

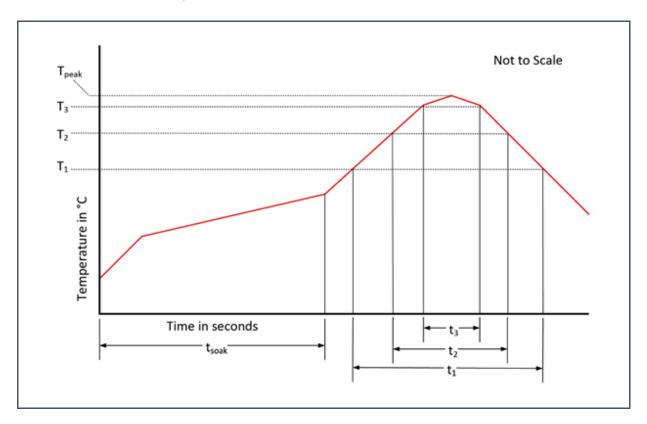

| 12                              | Soldering & Storage Information                                      | 94             |

| 12.1<br>12.2                    | Soldering InformationStorage Information                             |                |

| 13                              | Laser Eye Safety                                                     | 97             |

| 14                              | Revision Information                                                 | 98             |

| 15                              | Legal Information                                                    | 99             |

# 1 General Description

The TMF8820, TMF8821 & TMF8828 are a family of direct time-of-flight (dToF) sensors available in a small footprint modular package with integrated Vertical Cavity Surface Emitting Laser (VCSEL). The dToF device is based on SPAD, TDC and histogram technology and achieves 5000 mm detection range. Due to its lens on the SPAD, it supports 3x3, 4x4, 3x6 and 8x8 multizone output data and a very wide, dynamically adjustable, field of view. A multi-lens-array (MLA) inside the package above the VCSEL widens up the FoI (field of illumination). All processing of the raw data is performed on-chip and the TMF8820/21/28 provide distance information together with confidence values on its I<sup>2</sup>C interface.

TMF8820 3x3 zones operation

TMF8821 3x3, 4x4 and 3x6 zones operation TMF8828 3x3, 4x4, 3x6, and 8x8 zones operation

#### Information (only pertains to TMF8828)

The TMF8828 requires unique firmware (different from TMF8820/21/28) that will only operate on the TMF8828. The TMF8828 has two operating modes. It can operate as a TMF8820/21/28 (3x3, 4x4, or 3x6 zones) or in the TMF8828 mode which has 8x8 zones. In the TMF8828 mode, the device implements the 8x8 zone functionality as a sequence of four time-multiplexed measurements of 4x4 zones (like TMF8821). As such, the factory calibration sequence, loading the calibration data, reading the result measurements, and the optional histogram readouts must be performed four times in sequence by the host (please see the Host Driver Communication manual for details). The maximum measurement cycle rate in the TMF8828 mode is 15 Hz with 125 k iterations. Slower cycle rates with an increased number of iterations are possible.

## 1.1 Key Benefits & Features

The benefits and features of TMF8820/21/28, Multizone Time-of-Flight Sensor, are listed below:

Figure 1: Added Value of Using TMF8820/21/28

| Benefits                                              | Features                                   |

|-------------------------------------------------------|--------------------------------------------|

| Small footprint fits within narrow bezel applications | Modular package - 2.0 mm x 4.6 mm x 1.4 mm |

| Detecting objects in a very wide field of view        | 63° Fol/FoV                                |

| Benefits                                                                                                | Features                                                                                                                                    |

|---------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| Enable new applications like click to focus, object tracking, presence detection                        | TMF8828: Multizone with 3x3, 4x4, 3x6 and 8x8 zones TMF8821: Multizone with 3x3, 4x4 and 3x6 zones TMF8820: Multizone with 3x3 zones        |

| Within ±3% / ±10 mm of measurement (accuracy); no multipath and no multiple object problems as for iToF | Time-to-Digital Converter (TDC) Direct Time-of-Flight Measurement                                                                           |

| Better accuracy detects reliably closest object Minimum distance 10 mm Maximum distance 5000 mm         | Single Photon Avalanche Photodiode (SPAD) Histogram based architecture                                                                      |

| No complex calibration                                                                                  | Dynamic cover glass calibration                                                                                                             |

| Compensates for dirt on glass                                                                           | Reliable operation under demanding use cases                                                                                                |

| Improved accuracy over temperature and life                                                             | Reference SPAD                                                                                                                              |

| Make better decisions                                                                                   | Distance and signal quality reported                                                                                                        |

| Class 1 eye safe                                                                                        | Fast VCSEL driver with protection                                                                                                           |

| Integration flexibility                                                                                 | I <sup>3</sup> C tolerant - operate on a shared I <sup>2</sup> C / I <sup>3</sup> C bus                                                     |

| Longer battery life                                                                                     | 141 mW power consumption at 30 Hz operation 8 μA power consumption standby current (keep memory) 2 μA power-down current consumption (EN=0) |

# 1.2 Applications

The device is ideal for use with applications including:

- Distance measurement for camera autofocus Laser Detect Autofocus LDAF (mobile phone)

- Presence detection (computing and communication)

- Object detection and collision avoidance (robotics)

- Light curtain (industrial)

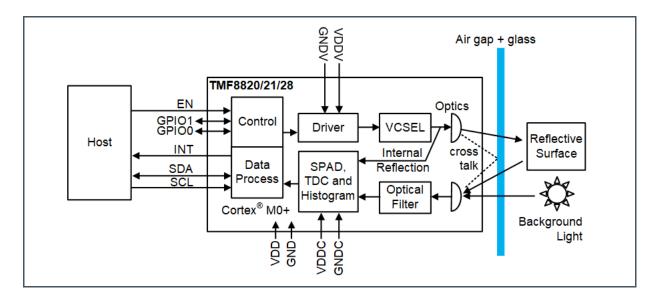

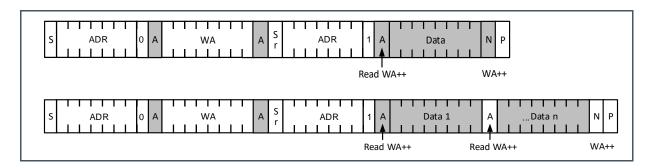

## 1.3 Block Diagram

The functional blocks of this device are shown below:

Figure 2 : Functional Blocks of TMF8820/21/28

# 2 Ordering Information

| Ordering Code | Package | Marking       | Delivery Form              | Delivery<br>Quantity | Note               |

|---------------|---------|---------------|----------------------------|----------------------|--------------------|

| TMF8820-1AM   |         |               | Tape & Reel<br>(7" reels)  | 500 pcs/reel         | - 3x3 zones        |

| TMF8820-1A    | _       |               | Tape & Reel<br>(13" reels) | 4000 pcs/reel        | - 3x3 zuries       |

| TMF8821-1AM   | - '     | tical 8-digit | Tape & Reel<br>(7" reels)  | 500 pcs/reel         | 3x3, 4x4 and       |

| TMF8821-1A    |         | tracecode     | Tape & Reel<br>(13" reels) | 4000 pcs/reel        | 3x6 zones          |

| TMF8828-1AM   | _       |               | Tape & Reel<br>(7" reels)  | 500 pcs/reel         | 3x3, 4x4, 3x6      |

| TMF8828-1A    | _       |               | Tape & Reel<br>(13" reels) | 4000 pcs/reel        | – and 8x8<br>zones |

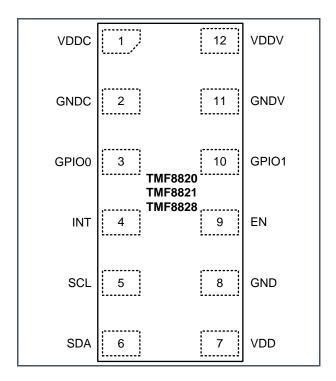

# 3 Pin Assignment

# 3.1 Pin Diagram

Figure 3: Pin Locations Top Through View (not to scale)

## 3.2 Pin Description

Figure 4: Pin Description of TMF8820/21/28

| Pin Number | Pin Name | Pin Type <sup>(1)</sup> | Description                                                                                                                            |

|------------|----------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| 1          | VDDC     | PWR                     | Charge pump supply voltage (3 V) – connect all VDD pins together; add a capacitor GRM155R70J104KA01 (0402 X7R 0.1 $\mu$ F 6.3V) to GND |

| 2          | GNDC     | GND                     | Charge pump ground; connect all ground pins together                                                                                   |

| 3          | GPIO0    | I/O                     | General purpose input/output; default tristate; connect to GND if not used                                                             |

| 4          | INT      | OD                      | Interrupt. Open-drain output; connect to GND if not used                                                                               |

| 5          | SCL      | IN                      | I <sup>2</sup> C serial clock                                                                                                          |

| 6          | SDA      | I/O                     | I <sup>2</sup> C serial data                                                                                                           |

| 7          | VDD      | PWR                     | Chip supply voltage (3 V) – connect all VDD pins together; add a capacitor GRM155R70J104KA01 (0402 X7R 0.1 µF 6.3 V) to GND            |

| 8          | GND      | GND                     | Chip ground; connect all ground pins together                                                                                          |

| 9          | EN       | IN                      | Enable input active high; setting to low forces the device into shutdown and all memory content is lost; connect to VDD if not used    |

| 10         | GPIO1    | I/O                     | General purpose input/output; default tristate; connect to GND if not used                                                             |

| 11         | GNDV     | GND                     | VCSEL ground; connect all ground pins together                                                                                         |

| 12         | VDDV     | PWR                     | VCSEL supply voltage (3 V) – connect all VDD pins together; add a capacitor GRM155R70J104KA01 (0402 X7R 0.1 µF 6.3 V) to GND           |

|            |          |                         |                                                                                                                                        |

(1) Explanation of abbreviations:

IN Digital input pin

I/O Digital Input output pin

OD Open drain output pin

GND ground supply pin

PWR Power Supply pin

#### Information

SDA, SCL, INT and EN have no diode to any VDD supply. Therefore even with VDD=0 V they do not block the interrupt line or  $I^2C$  bus.

GPIO0 and GPIO1 are push/pull output and have a diode to VDD; therefore if VDD is not powered, GPIO0 and GPIO1 shall not be driven from outside.

# 4 Absolute Maximum Ratings

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at these or any other conditions beyond those indicated under "Operating Conditions" is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Figure 5

Absolute Maximum Ratings of TMF8820/21/28

| Symbol              | Parameter                              | Min  | Max                | Unit | Comments                                                                                          |  |  |  |  |

|---------------------|----------------------------------------|------|--------------------|------|---------------------------------------------------------------------------------------------------|--|--|--|--|

| Electrical Pa       | Electrical Parameters                  |      |                    |      |                                                                                                   |  |  |  |  |

| $V_{DDMAX}$         | 3 V Supply Voltage to Ground           | -0.3 | 3.6 <sup>(1)</sup> | V    | Pins VDDV, VDDC, VDD                                                                              |  |  |  |  |

| $V_{GND}$           | Ground                                 | (    | 0.0                | V    | Pins GNDV, GNDC, GND                                                                              |  |  |  |  |

| V <sub>IOMAX</sub>  | Digital I/O Terminal Voltage           | -0.3 | 3.6                | V    | SCL, SDA, INT and EN;<br>has no internal diode to<br>VDD                                          |  |  |  |  |

| $V_{IO\_GPIO\_MAX}$ | Interface Digital I/O terminal voltage | -0.3 | VDD+0.3<br>max 3.6 | V    | GPIO0, GPIO1 has an internal diode to VDD                                                         |  |  |  |  |

| I <sub>SCR</sub>    | Input Current (latch-up immunity)      | ±    | ± 100              |      | JEDEC JESD78E                                                                                     |  |  |  |  |

| Electrostatio       | Discharge                              |      |                    |      |                                                                                                   |  |  |  |  |

| ESD <sub>HBM</sub>  | Electrostatic Discharge HBM            | ± 2  | 2000               | V    | JS-001-2017                                                                                       |  |  |  |  |

| ESD <sub>CDM</sub>  | Electrostatic Discharge CDM            | ±    | 500                | V    | JEDEC JS-002-2018                                                                                 |  |  |  |  |

| Temperature         | Ranges and Storage Conditions          |      |                    |      |                                                                                                   |  |  |  |  |

| T <sub>STRG</sub>   | Storage Temperature Range              | -40  | 85                 | °C   |                                                                                                   |  |  |  |  |

| T <sub>BODY</sub>   | Package Body Temperature               |      | 260                | °C   | IPC/JEDEC J-STD-020(2)                                                                            |  |  |  |  |

| RH <sub>NC</sub>    | Relative Humidity (non-condensing)     | 5    | 85                 | %    |                                                                                                   |  |  |  |  |

| MSL                 | Moisture Sensitivity Level             | 3    |                    |      | Represents a maximum floor life time of 168h with T <sub>A</sub> <30 °C and RH <sub>NC</sub> <60% |  |  |  |  |

<sup>(1)</sup> Limit supply rise to 1 V/μs

<sup>(2)</sup> The reflow peak soldering temperature (body temperature) is specified according to IPC/JEDEC J-STD-020 "Moisture/Reflow Sensitivity Classification for Nonhermetic Solid State Surface Mount Devices." The lead finish for Pb-free leaded packages is "Matte Tin" (100 % Sn)

# **5** Electrical Characteristics

Device parameters are guaranteed at nominal conditions unless otherwise noted. While the device is operational across the temperature range, functionality will vary with temperature. The parameters with Min and Max values are guaranteed with production tests or SQC (Statistical Quality Control) methods.

Figure 6: Electrical Characteristics of TMF8820/21/28

| Symbol                       | Parameter                                         | Conditions                                                                                                                                                                                                                                 | Min  | Тур | Max | Unit |

|------------------------------|---------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|-----|------|

| VDD                          | 3 V supply voltage                                | Pins VDDV, VDDC and VDD                                                                                                                                                                                                                    | 2.7  | 3.0 | 3.3 | V    |

| VIO                          | I/O supply voltage                                | Supply voltage for external pull-up for SCL, SDA and INT.                                                                                                                                                                                  | 1.62 | 1.8 | 3.3 | V    |

| Т <sub>АМВ</sub>             | Operating ambient temperature                     |                                                                                                                                                                                                                                            | -30  | 23  | 70  | °C   |

| Current Consur               | nption                                            |                                                                                                                                                                                                                                            |      |     |     |      |

| I <sub>POWER_DOWN</sub>      | Power down current                                | Pin EN=0; state: power down;<br>T <sub>AMB</sub> =23°C                                                                                                                                                                                     |      | 2   | 10  | μΑ   |

| Istandby                     | Standby current                                   | Current consumption for PON=0, wakeup by special I <sup>2</sup> C command, only retention RAM keeps content; state: standby; I/O pins not toggling Only register 0xE0 (ENABLE) accessible by I <sup>2</sup> C interface when in this mode. |      | 8   |     | μΑ   |

| I <sub>STANDBY_TIMED</sub>   | Standby timed current                             | Current consumption for waiting for measurement period to expire. goto_standby_timed = 1, low_power_osc_on = 1 Only register 0xE0 (ENABLE) accessible by I <sup>2</sup> C interface when in                                                |      | 34  |     | μА   |

|                              |                                                   | this mode                                                                                                                                                                                                                                  |      |     |     |      |

| I <sub>WAIT</sub>            | Wait current                                      | Wakeup by I <sup>2</sup> C or timer, all<br>memories keep content, CPU off,<br>oscillator on;<br>state: wait                                                                                                                               |      | 216 |     | μΑ   |

| I <sub>ACTIVE</sub>          | Active current                                    | Current consumption for CPU running at 80 MHz, VCSEL and TDC off state: active – histogram processing                                                                                                                                      |      | 2.8 |     | mA   |

| I <sub>ACTIVE_</sub> RANGING | Active current for ranging (VCSEL emitting light) | Current consumption for CPU running at 80 MHz, VCSEL and TDC on state: active – ranging                                                                                                                                                    |      | 57  |     | mA   |

| Average Curren               | nt Consumption for Run                            | ning Application                                                                                                                                                                                                                           |      |     |     |      |

| P <sub>RANGING_AVG</sub>     | Average power consumption                         | Default settings with 550 k iterations, 3x3 mode, output data rate 30 Hz                                                                                                                                                                   |      | 141 |     | mW   |

| P <sub>RANGING_AVG_LP</sub>  | Average power consumption low power               | Output data rate 30 Hz, 3x3 mode, 50 k iterations                                                                                                                                                                                          |      | 19  |     | mW   |

| Symbol                           | Parameter                                    | Conditions                                                                      | Min  | Тур                   | Max  | Unit |

|----------------------------------|----------------------------------------------|---------------------------------------------------------------------------------|------|-----------------------|------|------|

| I/O Levels – Ove                 | er Temperature and Sup                       | ply                                                                             |      |                       |      |      |

| I <sub>LEAK</sub>                | Leakage current to VDD or GND                | SDA, SCL, GPIO0/1, EN, INT                                                      | -5   |                       | 5    | μΑ   |

| V <sub>IH</sub>                  | Input voltage high                           | SDA, SCL, GPIO0/1, EN                                                           | 1.26 |                       | 3.3  | V    |

| V <sub>IL</sub>                  | Input voltage low                            | SDA, SCL, GPIO0/1, EN                                                           | 0    |                       | 0.54 | V    |

| V <sub>OL2mA</sub>               | Output voltage low                           | SDA, INT, 2 mA sink                                                             | 0    |                       | 0.36 | V    |

| $V_{OL4mA}$                      | Output voltage low                           | SDA. INT, 4 mA sink                                                             | 0    |                       | 0.6  | V    |

| I <sub>DRIVE_H</sub>             | Output current high                          | 1 V applied on GPIO0/1                                                          | 3.6  |                       |      | mA   |

| I <sub>DRIVE_L</sub>             | Output current low                           | 1 V applied on GPIO0/1                                                          | 3.6  |                       |      | mA   |

| Timings – over                   | Temperature and Supply                       | /                                                                               |      |                       |      |      |

| f <sub>clk</sub>                 | RC oscillator                                | All internal timings are derived from this clock                                | 4.85 | 5                     | 5.15 | MHz  |

| f <sub>CPUclk</sub>              | Maximum operating frequency of CPU           | The CPU can be switched between fclk and fclk*16                                |      | fclk * 16<br>(80 MHz) |      | MHz  |

| VCSEL <sub>CLK</sub>             | Clock frequency of<br>VCSEL clock            |                                                                                 |      | 17.77                 |      | MHz  |

| t <sub>POR</sub>                 | Power on time                                | EN=1 to ready for I <sup>2</sup> C command                                      |      |                       | 2    | ms   |

|                                  | Time to download                             | For 1 MHz I <sup>2</sup> C speed [TMF8820/21]                                   |      | 50                    |      | ms   |

| t <sub>FW_DOWNLOAD</sub>         | firmware                                     | For 1 MHz I <sup>2</sup> C speed [TMF8828]                                      |      | 100                   |      | ms   |

| t <sub>FIRST_MEAS_COLD</sub>     | Time from cold start to first measurement    | From EN=0->1 (power down) to first measurement result; default settings (33 ms) |      | 190                   |      | ms   |

| t <sub>FIRST_MEAS_WARM</sub>     | Time from warm start to first measurement    | From standby to first measurement result; default settings (33 ms)              |      | 60                    |      | ms   |

| t <sub>SWITCH_to_8820/8821</sub> | Time to switch to TMF8820/21 mode            | From command 0x65 to CMD_STAT to first measurement result [TMF8828]             |      | 65                    |      | ms   |

| t <sub>SWITCH_to_8828</sub>      | Time to switch to TMF8828 mode               | From command 0x6C to CMD_STAT to first measurement result [TMF8828]             |      | 115                   |      | ms   |

| I <sup>2</sup> C Interface – o   | ver Temperature and Su                       | ıpply                                                                           |      |                       |      |      |

| f <sub>SCLK</sub>                | SCL clock frequency                          |                                                                                 | 0    | 400                   | 1000 | kHz  |

| t <sub>BUF</sub>                 | Bus free time<br>between a STOP and<br>START |                                                                                 | 0.5  |                       |      | μs   |

| t <sub>HD:STA</sub>              | Hold time<br>(Repeated) Start                |                                                                                 | 0.26 |                       |      | μs   |

| $t_{LOW}$                        | LOW period of SCL<br>Clock                   |                                                                                 | 0.5  |                       |      | μs   |

| t <sub>HIGH</sub>                | HIGH period of SCL clock                     |                                                                                 | 0.26 |                       |      | μs   |

| t <sub>SU:STA</sub>              | Setup time for a<br>Repeated START           |                                                                                 | 0.26 |                       |      | μs   |

| t <sub>HD:DAT</sub>              | Data hold time                               |                                                                                 | 0    |                       |      | μs   |

| t <sub>SU:DAT</sub>              | Data setup time                              |                                                                                 | 50   |                       |      | ns   |

| -30.DA1                          |                                              |                                                                                 |      |                       |      |      |

| Symbol                            | Parameter                                         | Conditions                                         | Min     | Тур          | Max        | Unit    |

|-----------------------------------|---------------------------------------------------|----------------------------------------------------|---------|--------------|------------|---------|

| t <sub>F</sub>                    | Fall time of both SDA and SCL                     |                                                    | 20      |              | 120        | ns      |

| Optical Paramet                   | ters                                              |                                                    |         |              |            |         |

| Fol                               | Field of view of the illuminator main area        | Diagonal, FWHM <sup>(3)</sup> of radiant intensity | See sec | tion 7.5.2   |            |         |

| Optical Multizor                  | ne Parameters                                     |                                                    |         |              |            |         |

| SPAD <sub>X</sub>                 | Delta in angle of single SPAD in x                | In optical center                                  |         | 2.4          |            | degrees |

| SPAD <sub>Y</sub>                 | Delta in angle of single SPAD in y <sup>(1)</sup> | In optical center                                  |         | 5.6          |            | degrees |

| Optical Stack Re                  | Optical Stack Requirements                        |                                                    |         |              |            |         |

| GLASS <sub>TRANSPAR</sub><br>ENCY | Glass transparency<br>@ 940 nm                    | The device can work with IR inked or clear glass   | 85      | 90           |            | %       |

| XTALK <sub>SYSTEM</sub>           | System Crosstalk                                  | Measured in final application                      | See am  | s OSRAM opti | cal design | guide   |

<sup>(1)</sup> Due to SPADs with too high dark count, which are disabled by production test (screamer detection), need to use always at least two SPADs next to each other.

<sup>(2)</sup> FWHM – full width half maximum.

# **6 Typical Operating Characteristics**

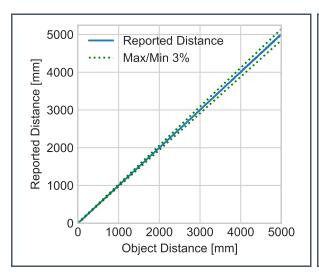

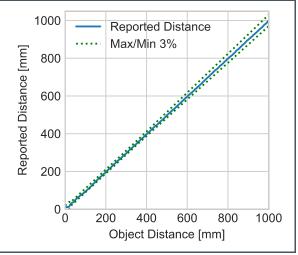

Following operating characteristics are measured with calibrated devices with full optical stack. The ambient light is measured on the target. The data is perpendicular scaled for the non-center zones.

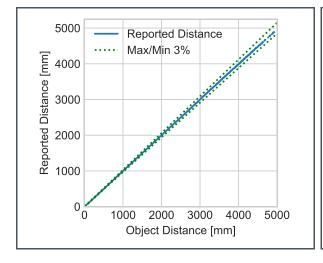

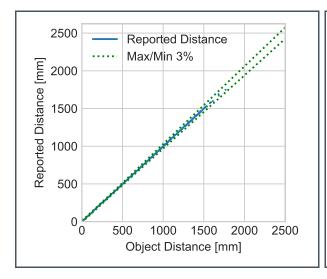

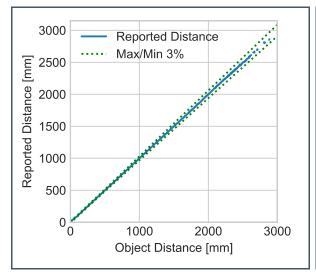

Figure 7: 350 Lux Fluorescent Light 18% Grey Card 3x3, 33°x32° FoV Center Zone, 30 Hz

Figure 8: Figure 7 Zoomed to 0 mm – 1000 mm

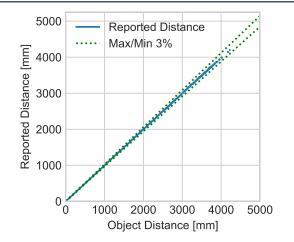

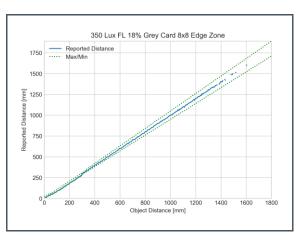

Figure 9: 350 Lux Fluorescent Light 18% Grey Card 3x3, 33°x32° FoV, Edge Zone, 30 Hz

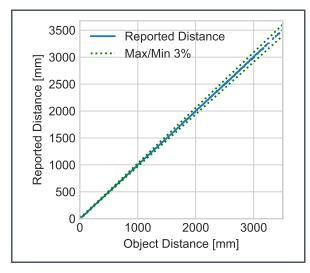

Figure 10: 350 Lux Fluorescent Light 18% Grey Card 3x3, 33°x32° FoV, Corner Zone, 30 Hz

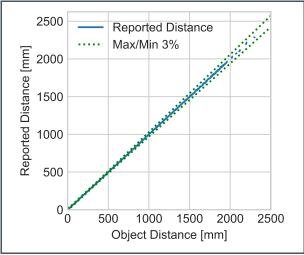

Figure 11: 140 Lux HAL (1 Lux sunlight) 18% Grey Card 3x3, 33°x32° FoV Center Zone, 30 Hz

Figure 12: 700 Lux HAL (5 k Lux sunlight) 18% Grey Card 3x3, 33°x32° FoV Center Zone, 30 Hz

Figure 13: 1400 Lux HAL (10 k Lux sunlight) 18% Grey Card 3x3, 33°x32° FoV Center Zone, 30 Hz

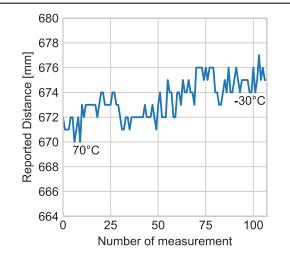

Figure 14:

Reported Distance During a Temperature

Sweep from 70 °C to -30 °C with a Fixed

Target in the Oven

## 6.1 4x4 Zones Operating Mode (only TMF8821 and TMF8828)

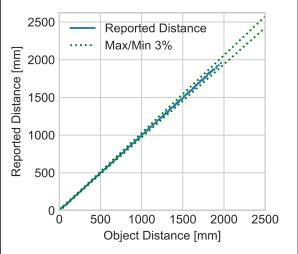

Figure 15: 350 Lux Fluorescent Light 18% Grey Card 4x4, 41°x52° FoV Center Zone, 15 Hz

Figure 16: Figure 15 Zoomed to 0 mm - 1000 mm

Figure 17: 350 Lux Fluorescent Light 18% Grey Card 4x4, 41°x52° FoV, Edge Zone, 15 Hz

Figure 18: 350 Lux Fluorescent Light 18% Grey Card 4x4, 41°x52° FoV, Corner Zone, 15 Hz

# 6.2 8x8 Zones Operating Mode (only TMF8828)

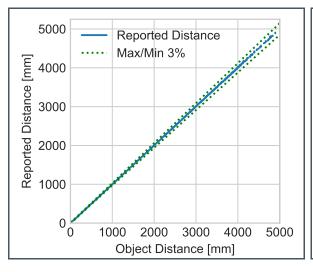

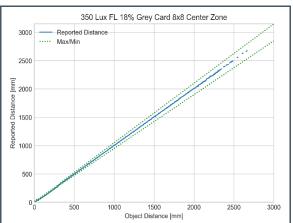

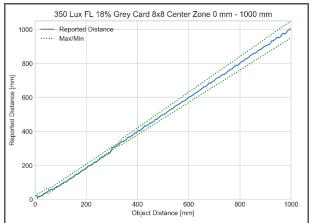

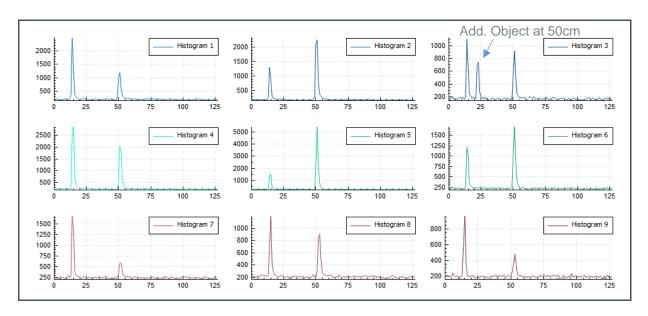

Figure 19: 350 Lux Fluorescent Light 18% Grey Card 8x8, 41°x52° FoV Center Zone, 15 Hz

Figure 20: Figure 19 Zoomed to 0 mm - 1000 mm

Figure 21: 350 Lux Fluorescent Light 18% Grey Card 8x8, 41°x52° FoV, Edge Zone, 15 Hz

Figure 22: 350 Lux Fluorescent Light 18% Grey Card 8x8, 41°x52° FoV, Corner Zone, 15 Hz

# 7 Functional Description

### 7.1 General Operating Description

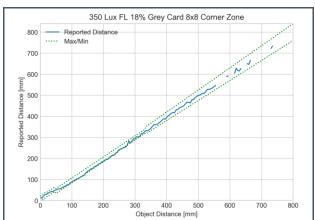

The TMF8820/21/28 operating principle uses a pulse train of VCSEL pulses defined by the iteration setting. These pulses are spread using a MLA (micro lens array) to illuminate the FoI (field of illumination). An object reflects these rays back to the TMF8820/21/28 receiver optics lens and onto a SPAD (single photon avalanche detector) array. A TDC (time to digital converter) measures now the time from emission of these pulses to their arrival and accumulates the hits into bins inside a histogram. As TMF8820/21 sends 550 k pulses (default settings), the output of the TDC is a full histogram as shown in Figure 23:

Figure 23: Example Target Histogram and Reference Histogram (Blue)

The large blue peak (clipped due to scaling for measurement peaks) in the histogram shows the reference peak histogram. A SPAD, which is located in the cavity of the VCSEL, generates this target peak. The target detection algorithm uses this peak together with the crosstalk peaks at bin 15 in the measurements channels to calculate zero distance. All measurement histograms show a crosstalk peak around bin 15 and the actual target peak at bin 50 – the algorithm has an internal calibration to calculate from bins to time, which the algorithm converts to distance using speed of light. In above example, the time from bin 15 to bin 50 represents a target distance of 2 m.

The internal processor (ARM M0+ ®) executes the ams OSRAM algorithm on these histograms to calculate the target distance of the object. The output of this calculation is the distance in [mm] presented on the I<sup>2</sup>C interface for each of the zones.

#### 7.1.1 Multizone / Multi-Object Functionality

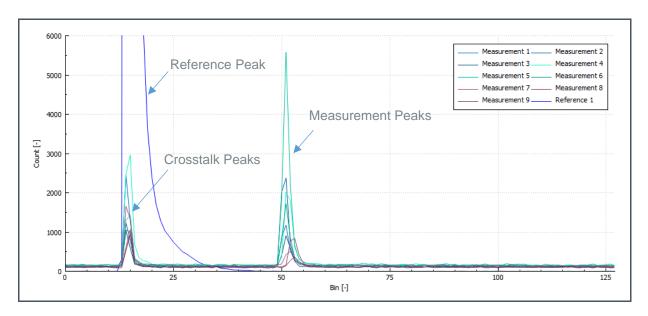

The SPADs below the receiver lens are in focus of this lens. Therefore, depending on the location of the object, the different zones see different areas of the scene as shown in the raw histogram graph in Figure 24:

Figure 24:

Multizone Histograms Example

In zone3 (histogram 3) there is an additional object at 50 cm which is shown by a third peak in the histogram around bin 25. Zone3 outputs a first object at 50 cm and a second object at 2 m distance.

# 7.2 Timing Diagrams

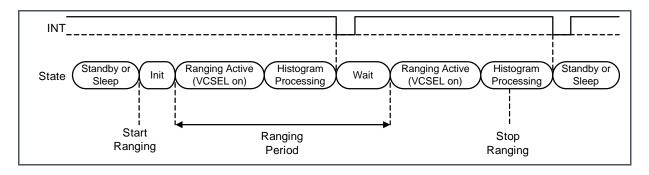

Following figure shows a typical target measurement timing diagram of TMF8820/21/28:

Figure 25:

Timing Diagram for Ranging Period > Ranging Active + Histogram Processing

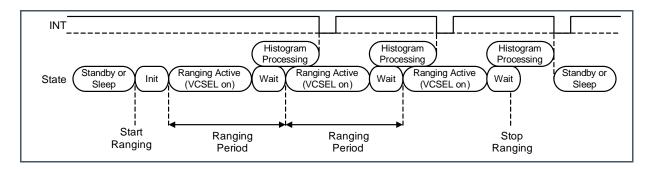

If the ranging period is chosen shorter than the combined time of ranging active and histogram processing, the TMF8820/21/28 automatically runs histogram processing in parallel to ranging active:

Figure 26:

Timing Diagram for Ranging Period < Ranging Active + Histogram Processing

#### Note:

In time multiplex mode for TMF8821 (4x4 and 3x6) and TMF8828 (8x8), ranging active is executed 2 times for 3x6 and 4x4 respectively 4 times for 8x8 mode before an interrupt is sent after histogram processing. Each VCSEL burst uses the programmed number of iterations defined by register iterations[15:8] and iterations[7:0].

#### 7.3 Calibration

To achieve the performance described in the next sections, the correct SPAD mask shall be set, iterations set to 4 M and calibration of the algorithm needs to be performed (cmd\_stat = 0x20). The TMF8820/21/28 shall be embedded in the final application and the cover glass including the IR ink needs to be assembled. The calibration test shall be done in a housing with minimal ambient light and no target within 40 cm in field of view of the TMF8820/21/28.

#### **Attention**

Set number of iterations during calibration to 4 M to ensure accuracy. Read also the optical design guide (ODG) to have the system crosstalk level in the range defined by this document.

The TMF8820/21/28 generates a calibration data set, which needs to be stored on the host processor and reloaded after each power down or reset event.

It shall be ensured by the optical design that the optical crosstalk values are meeting the limits defined in the TMF8820/21/28 optical design guide (ODG).

Figure 27:

Calibration Data Measured Crosstalk Values (Little endian format = LSB first)

| l <sup>2</sup> C Address<br>(if appid=0x03,<br>cid_rid=0x19 –<br>Factory Calibration) | Offset in Calibration<br>Data File | Meaning                                                                                                                                                                 |

|---------------------------------------------------------------------------------------|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x2A-0x2B                                                                             | 0x06-0x07                          | Iterations used for calibration divided by 1024                                                                                                                         |

|                                                                                       |                                    | e multiplexed mode (3x3); also for the first d 3x6); TMF8828 repeats 4x4 calibration 4 times                                                                            |

| 0x5C-0x5F                                                                             | 0x38-0x3B                          | Crosstalk for reference channel – shall be ignored                                                                                                                      |

| 0x60-0x63                                                                             | 0x3C-0x3F                          | Crosstalk for channel 1                                                                                                                                                 |

| 0x64-0x67                                                                             | 0x40-0x43                          | Crosstalk for channel 2                                                                                                                                                 |

| 0x68-0x6B                                                                             | 0x44-0x47                          | Crosstalk for channel 3                                                                                                                                                 |

| 0x6C-0x6F                                                                             | 0x48-0x4B                          | Crosstalk for channel 4                                                                                                                                                 |

| 0x70-0x73                                                                             | 0x4C-0x4F                          | Crosstalk for channel 5                                                                                                                                                 |

| 0x74-0x77                                                                             | 0x50-0x53                          | Crosstalk for channel 6                                                                                                                                                 |

| 0x78-0x7B                                                                             | 0x54-0x57                          | Crosstalk for channel 7                                                                                                                                                 |

| 0x7C-0x7F                                                                             | 0x58-0x5B                          | Crosstalk for channel 8                                                                                                                                                 |

| 0x80-0x83                                                                             | 0x5C-0x5F                          | Crosstalk for channel 9                                                                                                                                                 |

|                                                                                       |                                    | s 1-9 only for the second measurement in time ats 4x4 calibration 4 times                                                                                               |

| 0xB4-0xB7                                                                             | 0x90-0x93                          | Crosstalk for reference channel; time multiplex – shall be ignored                                                                                                      |

| 0xB8-0xBB                                                                             | 0x94-0x97                          | Crosstalk for channel 1; time multiplex                                                                                                                                 |

| 0xBC-0xBF                                                                             | 0x98-0x9B                          | Crosstalk for channel 2; time multiplex                                                                                                                                 |

| 0xC0-0xC3                                                                             | 0x9C-0x9F                          | Crosstalk for channel 3; time multiplex                                                                                                                                 |

| 0xC4-0xC7                                                                             | 0xA0-0xA3                          | Crosstalk for channel 4; time multiplex                                                                                                                                 |

| 0xC8-0xCB                                                                             | 0xA4-0xA7                          | Crosstalk for channel 5; time multiplex                                                                                                                                 |

| 0xCC-0xCF                                                                             | 0xA8-0xAB                          | Crosstalk for channel 6; time multiplex                                                                                                                                 |

| 0xD0-0xD3                                                                             | 0xAC-0xAF                          | Crosstalk for channel 7; time multiplex                                                                                                                                 |

| 0xD4-0xD7                                                                             | 0xB0-0xB3                          | Crosstalk for channel 8; time multiplex                                                                                                                                 |

| 0xD8-0xDB                                                                             | 0xB4-0xB7                          | Crosstalk for channel 9; time multiplex                                                                                                                                 |

| 0xDC                                                                                  | 0xB8                               | fc_status_during_cal - calibration status during factory calibration – copy of register 0x07 – 0x00 success, all other values are reporting an error during calibration |

The host shall send the calibration data for the selected SPAD mask on each power-up of the TMF8820/21/28 and after each change of the SPAD mask using cmd\_stat = 0x19, prior to execution of the ams OSRAM algorithm.

#### Attention

Calibration shall be done individually for all different SPAD masks used in operation of the device.

### 7.4 Algorithm Performance

The algorithm performance is measured using the driver supplied by ams OSRAM and using the latest firmware included in TMF882x\_Driver\_Linux\_v\*.zip. Download the latest firmware from **ams** website:

- For TMF8820 see https://ams.com/tmf8820

- For TMF8821 see https://ams.com/tmf8821

- For TMF8828 see https://ams.com/tmf8828

The driver automatically performs clock skew correction (use host clock to compensate for the TMF8820/21/28 internal clock drift) to achieve the accuracy.

See also section 9.5 for available drivers.

Performance parameters apply at nominal supply and temperature.

#### 7.4.1 SPAD Mask and Mode Selection

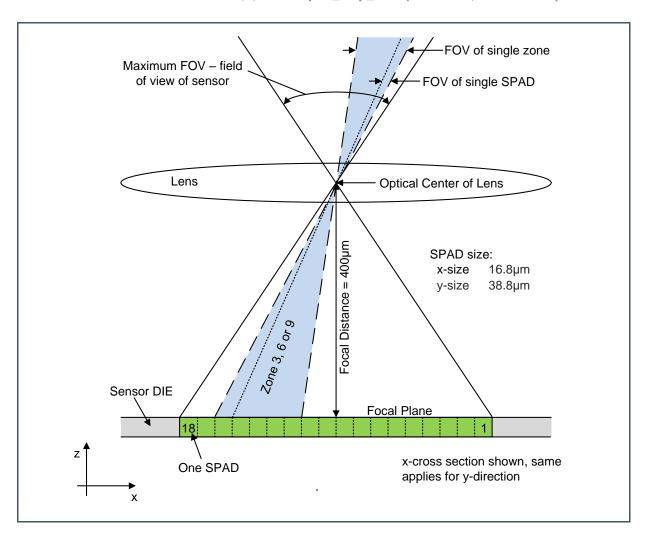

The SPAD mask selection (register spad\_map\_id see Figure 113) defines the assignment of the SPADs to the individual zones – due to the lens above the SPADs, the FoV (field of view) of the sensor is also defined by the SPAD mask as shown in Figure 29.

The ranging period shown in Figure 28 is depending on the operating mode, which is selected by spad\_map\_id and the iterations setting, set by register iterations. To achieve fastest ranging period set the report period in ms (register period) below ranging period to ensure that there will be no wait time.

Figure 28:

Ranging Period vs. Iterations and Operating Mode

| Operating Mode | Iterations | Ranging Period With<br>No Wait Time Programmed |

|----------------|------------|------------------------------------------------|

|                | 50 k       | 6.1 ms                                         |

| 3x3            | 550 k      | 32.2 ms                                        |

|                | 4000 k     | 230 ms                                         |

| Operating Mode | Iterations | Ranging Period With<br>No Wait Time Programmed |

|----------------|------------|------------------------------------------------|

|                | 50 k       | 13 ms                                          |

| 3x6 or 4x4     | 550 k      | 65 ms                                          |

|                | 4000 k     | 460 ms                                         |

|                | 50 k       | 26 ms                                          |

| 8x8            | 550 k      | 129 ms                                         |

|                | 4000 M     | 920 ms                                         |

Figure 29:

Relation of SPADs to FoV – Zone 3,6,9 from spad\_map\_id=1 (3x3 mode, 33°x32° FoV)

FoV of a SPAD or a zone can be calculated with, assuming center of zone is in optical center:

#### **Equation 1:**

$$FoV \ [^{\circ}] = 2 * atan \frac{size \ of \ zone \ or \ SPAD}{2 * \ focal \ distance}$$

Where focal distance =  $400 \mu m$

Size of a single SPAD is 16.8 μm in x-direction and 38.8 μm in y-direction.

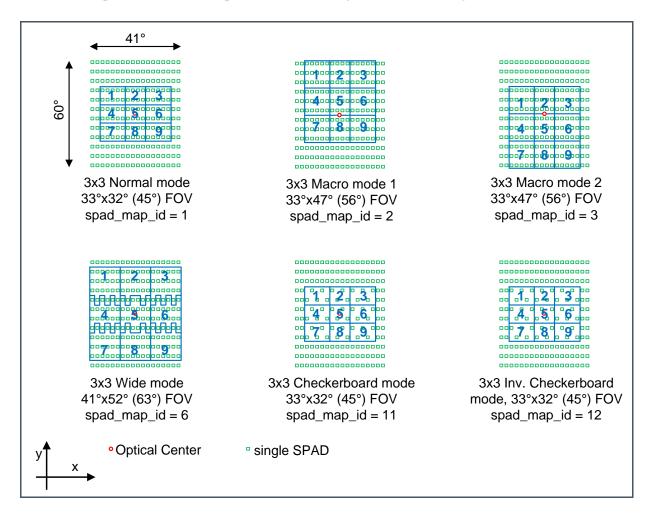

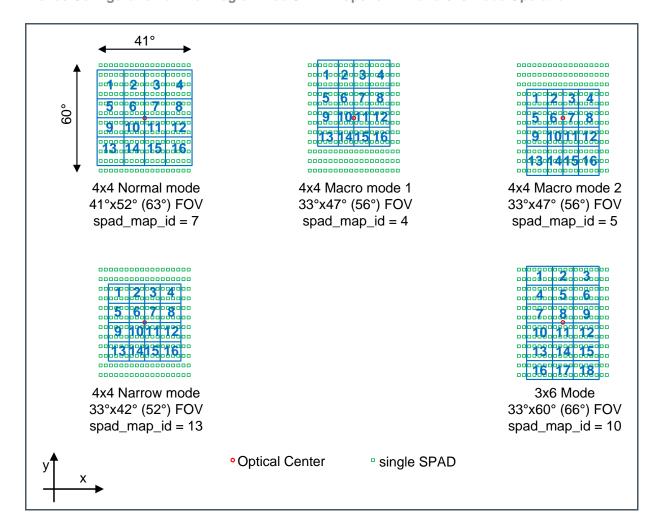

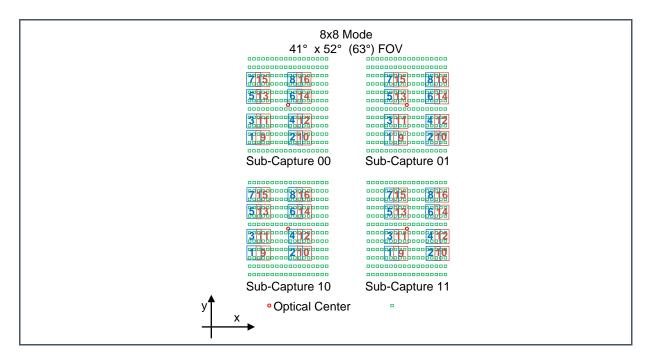

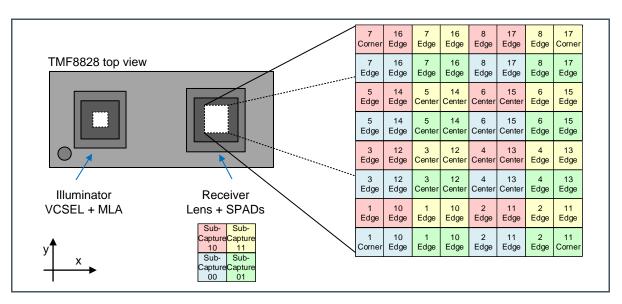

There are several pre-defined SPAD masks available as shown in Figure 113 and drawn in Figure 30 for 3x3 mode and Figure 31 for 4x4 and 3x6 mode and Figure 32 for 8x8 mode:

Figure 30:

Zones Configuration of Pre-Programmed SPAD Maps for 3x3 Mode Operation

Note: Use the checkerboard SPAD masks especially for high ambient light conditions.

Figure 31:

Zones Configuration of Pre-Programmed SPAD Maps for 4x4 and 3x6 Mode Operation

Figure 32:

Zones Configuration of Pre-Programmed SPAD Maps for 8x8 Mode Operation

Except in TMF8828 mode, the customer can design an own SPAD mask and assign SPADs to channels individually. In TMF8828 mode, the SPAD mask is fixed and cannot be changed. There are following constrains for these SPAD masks:

- Use spad\_map\_id=14 for single measurement up to 9 zones and spad\_map\_id=15 for time multiplexed measurement up to 18 zones

- The SPAD mask has a maximum size of 18x10.

- SPAD mapping and SPAD enable mask shall have the exact same size.

- Channel 0 is reserved for the reference channel and shall not be used in a SPAD mask.

- The resulting SPAD mask plus offset shall not exceed 18x12 example: An 18x10 size SPAD mask has to have x\_offset\_2=0 (18 is already the limit) but can have a y-offset of +/-1 SPAD. Please note that the actual register value y\_offset\_2 is multiplied by 2 so, +2 or -2 is the actual value stored to y\_offset\_2 to obtain an offset of +1 respectively -1.

- In each used channel, there shall be at least two adjacent SPADs (can be in any direction).

- A single row shall not use channel 1 and channel 8 or 9 at the same time.

- There needs to be at least one channel per TDC enabled otherwise electrical calibration will fail

use at minimum channel (2 or 3) and (4 or 5) and (6 or 7) and (8 or 9)

A complete SPAD mask consists of an enable mask, where a '1' is an enabled SPAD and a '0' is used for a disabled SPAD, and a TDC channel selection mask where the number '1'...'9' assigns this SPAD to a TDC channel. See document TMF882X\_Host\_Driver\_Communication\*.pdf for detailed explanation how to download customized SPAD maps.

ams OSRAM recommends to program the SPAD mask through the device driver and read back the masks for verification.

Whenever the SPAD mask selection is changed, the current calibration is no longer valid – see section 7.3.

#### **CAUTION**

For a user defined SPAD mask ensure that each zone has at least two adjacent SPADs enabled. Otherwise, on some devices this zone might not see any target counts at all.

#### 7.4.2 Performance in 3x3 Operating Mode

The algorithm reports distance information for each of the zone individually for the closest and the 2<sup>nd</sup> closest object in 1 mm steps. The algorithm performance is depending on the chosen zone:

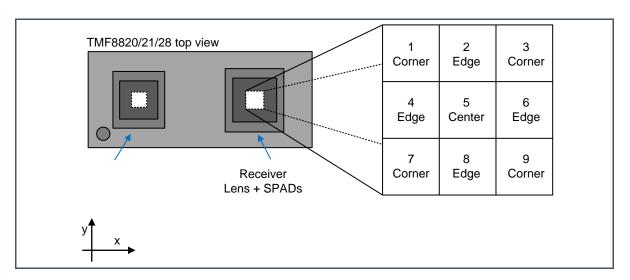

Figure 33: Zones Definition

For spad\_map\_id=1 (3x3 mode, 33°x32° FoV), calibration according to section 7.3, following performance parameters apply. The reported distance is the actual distance between the device and the actual measured zone – there is no perpendicular flat target correction applied. The target covers the full FoV of the device.

Figure 34:

Typical Maximum Distance in 3x3 Mode, 33°x32° FoV, 550 k Iterations (30 Hz output data rate),

Light on the Target Only

| Target<br>Reflectivity %T<br>at 940 nm | Zone   | 350 Lux LED<br>Lighting | 140 Lux<br>Halogen <sup>(1)</sup> | 700 Lux<br>Halogen <sup>(2)</sup> | 1400 Lux<br>Halogen <sup>(3)</sup> |

|----------------------------------------|--------|-------------------------|-----------------------------------|-----------------------------------|------------------------------------|

|                                        | Center | 5000 mm                 | 4500 mm                           | 2000 mm                           | 1000 mm                            |

| White target 90%                       | Edge   | 5000 mm                 | 4000 mm                           | 1800 mm                           | 950 mm                             |

|                                        | Corner | 5000 mm                 | 3000 mm                           | 1500 mm                           | 750 mm                             |

|                                        | Center | 5000 mm                 | 3000 mm                           | 2000 mm                           | 1500 mm                            |

| Grey target 18%                        | Edge   | 4500 mm                 | 2800 mm                           | 1500 mm                           | 1400 mm                            |

|                                        | Corner | 4000 mm                 | 2000 mm                           | 1400 mm                           | 1200 mm                            |

- (1) 140 lux halogen light represents 1 k lux sunlight

- (2) 700 lux halogen light represents 5 k lux sunlight

- (3) 1400 lux halogen light represents 10 k lux sunlight

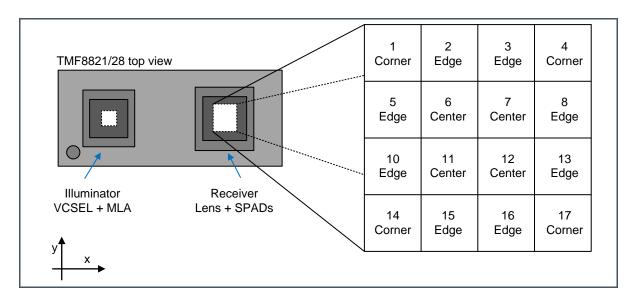

#### 7.4.3 Performance in 4x4 Operating Mode – Only TMF8821 and TMF8828

#### Information

Please note that the zones for 4x4 operating mode are presented in zones 1-8 and 10-17; the result for zone 9 and 18 is not used.

The algorithm reports distance information for each of the zone individually for the closest and the 2<sup>nd</sup> closest object in 1 mm steps. The algorithm performance is depending on the chosen zone:

Figure 35: Zones Definition (TMF8821 and TMF8828)

For spad\_map\_id=7 (4x4 mode, 41°x52° FoV), calibration according to section 7.3, following performance parameters apply. The reported distance is the actual distance between the device and the actual measured zone – there is no perpendicular flat target correction applied. The target covers the full FoV of the device.

Figure 36: Typical Maximum Distance in 4x4 Mode, 41°x52° FoV, 550 k Iterations (15 Hz output data rate), Light on the Target Only

| Target<br>Reflectivity %T<br>at 940 nm | Zone   | 350 Lux LED<br>Lighting | 140 Lux<br>Halogen <sup>(1)</sup> | 700 Lux<br>Halogen <sup>(2)</sup> | 1400 Lux<br>Halogen <sup>(3)</sup> |

|----------------------------------------|--------|-------------------------|-----------------------------------|-----------------------------------|------------------------------------|

|                                        | Center | 5000 mm                 | 3500 mm                           | 2000 mm                           | 1000 mm                            |

| White target 90%                       | Edge   | 3000 mm                 | 1400 mm                           | 900 mm                            | 500 mm                             |

|                                        | Corner | 2900 mm                 | 1300 mm                           | 800 mm                            | 400 mm                             |

|                                        | Center | 4000 mm                 | 2500 mm                           | 1500 mm                           | 1400 mm                            |

| Grey target 18%                        | Edge   | 1500 mm                 | 1200 mm                           | 800 mm                            | 700 mm                             |

|                                        | Corner | 1400 mm                 | 1100 mm                           | 700 mm                            | 600 mm                             |

- (1) 140 lux HAL represents 1k lux sunlight

- (2) 700 lux HAL represents 5k lux sunlight

- (3) 1400 lux HAL represents 10k lux sunlight

#### 7.4.4 Performance in 8x8 Operating Mode – Only TMF8828

#### Information

Please note that the zones for 8x8 operating mode are presented in zones 1-8 and 10-17; the result for zone 9 and 18 is not used.

The algorithm reports distance information for each of the zone individually for the closest and the 2<sup>nd</sup> closest object in 1 mm steps. The algorithm performance is depending on the chosen zone:

Figure 37: Zones Definition (TMF8828)

After calibration according to section 7.3, the following performance parameters apply. The reported distance is the actual distance between the device and the actual measured zone – there is no perpendicular flat target correction applied. The target covers the full FoV of the device.

Figure 38: Typical Maximum Distance in 8x8 Mode, 41°x52° FoV, 125 k Iterations (15 Hz output data rate), Light on the Target Only

| Target<br>Reflectivity %T<br>at 940 nm | Zone   | 350 Lux LED<br>Lighting | 140 Lux<br>Halogen <sup>(1)</sup> | 700 Lux<br>Halogen <sup>(2)</sup> | 1400 Lux<br>Halogen <sup>(3)</sup> |

|----------------------------------------|--------|-------------------------|-----------------------------------|-----------------------------------|------------------------------------|

|                                        | Center | 4400 mm                 | 2000 mm                           | 1300 mm                           | 1000 mm                            |

| White target 90%                       | Edge   | 1500 mm                 | 900 mm                            | 500 mm                            | 400 mm                             |

|                                        | Corner | 900 mm                  | 600 mm                            | 300 mm                            | 300 mm                             |

| Target<br>Reflectivity %T<br>at 940 nm | Zone   | 350 Lux LED<br>Lighting | 140 Lux<br>Halogen <sup>(1)</sup> | 700 Lux<br>Halogen <sup>(2)</sup> | 1400 Lux<br>Halogen <sup>(3)</sup> |

|----------------------------------------|--------|-------------------------|-----------------------------------|-----------------------------------|------------------------------------|

|                                        | Center | 2000 mm                 | 1500 mm                           | 1000 mm                           | 800 mm                             |

| Grey target 18%                        | Edge   | 800 mm                  | 600 mm                            | 400 mmm                           | 300 mm                             |

|                                        | Corner | 500 mm                  | 400 mm                            | 300 mm                            | 200 mm                             |

- (1) 140 lux HAL represents 1k lux sunlight

- (2) 700 lux HAL represents 5k lux sunlight

- (3) 1400 lux HAL represents 10k lux sunlight

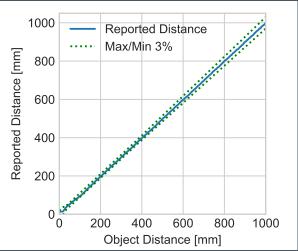

#### 7.4.5 Short Range High Accuracy Mode

From EVM release 3v52 onwards, the TMF8820/21/28 have a short range and high accuracy mode. This operating mode enhances the accuracy for a detection range up to 1000 mm.

Use this operating mode only if best accuracy for short range is needed as this operating mode reduces maximum detection distance as shown by Figure 34, Figure 36 and Figure 38 by approximately 50 % and clips it to 1000 mm but greatly enhances accuracy.

The mode can be enabled by setting of register active\_range. Please download the relevant calibration data after switching the operating mode.

Figure 39: Accuracy Short Range Mode of TMF8820/21/28

| Symbol           | Parameter                      | Conditions                                    | Min | Тур    | Max | Unit |

|------------------|--------------------------------|-----------------------------------------------|-----|--------|-----|------|

|                  | Minimum                        | Grey target 18%                               |     | 10     |     | mm   |

| dміn             | detection<br>distance          | White target 90%                              |     | 25     |     | mm   |

|                  |                                | 10 mm to 20 mm                                |     | ± 10   |     | mm   |

|                  | Accuracy of                    | 20 mm to 200 mm                               |     | ± 5    |     | mm   |

| daccuracy3x3,4x4 | detection for 3x3 and 4x4 mode | 200 mm to 1000 mm; all except corner zones    |     | ± 2.0  |     | %    |

|                  |                                | 200 mm to 1000 mm; corner zones               |     | ± 2.5  |     | %    |

|                  |                                | 10 mm to 20 mm                                |     | ± 10   |     | mm   |

|                  |                                | 20 mm to 40 mm                                |     | ± 5    |     | mm   |

| daccuracy8x8     | Accuracy of<br>detection for   | 40 mm to 100 mm                               |     | -10/+5 |     | mm   |

|                  | 8x8 mode                       | 100 mm to 200 mm                              |     | ± 5    |     | mm   |

|                  |                                | 200 mm to 1000 mm;<br>all except corner zones |     | ± 2.0  |     | %    |

| Symbol     | Parameter | Conditions                               | Min | Тур            | Max | Unit |

|------------|-----------|------------------------------------------|-----|----------------|-----|------|

|            |           | 200 mm to 1000 mm; corner zones          |     | ± 3.0          |     | %    |

| dprecision | Precision | ± 2 sigma (95%),<br>350 lux LED lighting |     | 2 mm<br>+ 0.5% |     |      |

#### **Attention**

The short range, high accuracy mode needs an individual calibration per SPAD map – see document TMF882X\_Host\_Driver\_Communication\*.pdf for detailed explanation of this calibration.

#### 7.4.6 Accuracy / Precision Long Range Mode (default)

Figure 40:

Accuracy and Precision Parameters Long Range Mode (TMF8820/21 mode – 550 k iterations)

| Symbol                 | Parameter                  | Conditions                               | Min | Тур            | Max | Unit |

|------------------------|----------------------------|------------------------------------------|-----|----------------|-----|------|

| d <sub>MIN</sub>       | Minimum detection distance |                                          |     | 10             |     | mm   |

|                        |                            | 10 mm to 20 mm                           |     | ± 19           |     | mm   |

|                        | Accuracy of detection      | 20 mm to 50 mm,<br>grey target           |     | ± 10           |     | mm   |

| daccuracy              |                            | 50 mm to 250 mm                          |     | ± 15           |     | mm   |

|                        |                            | 250 mm to 333 mm                         |     | ± 10           |     | mm   |

|                        |                            | ≥ 333 mm                                 |     | ± 3            |     | %    |

| d <sub>PRECISION</sub> | Precision                  | ± 2 sigma (95%),<br>350 lux LED lighting |     | 2 mm<br>+ 0.5% |     |      |

Please note that above parameters are typical parameters and perpendicular flat target correction applied.

Figure 41:

Accuracy and Precision Parameters Long Range Mode (TMF8828 mode – 125 k iterations)

| Symbol           | Parameter                  | Conditions     | Min | Тур    | Max | Unit |

|------------------|----------------------------|----------------|-----|--------|-----|------|

| d <sub>MIN</sub> | Minimum detection distance |                |     | 10     |     | mm   |

| daccuracy        | Accuracy of detection      | 10 mm to 20 mm |     | -4/+22 |     | mm   |

| Symbol     | Parameter | Conditions                               | Min | Тур            | Max | Unit |

|------------|-----------|------------------------------------------|-----|----------------|-----|------|

|            |           | 20 mm to 50 mm,<br>grey target           |     | -3/+18         |     | mm   |

|            |           | 50 mm to 250 mm                          |     | -16/+7         |     | mm   |

|            |           | 250 mm to 333 mm                         |     | -12/+7         |     | mm   |

|            |           | ≥ 333 mm                                 |     | ± 5            |     | %    |

| dPRECISION | Precision | ± 2 sigma (95%),<br>350 lux LED lighting |     | 2 mm<br>+ 0.5% |     |      |

Please note that above parameters are typical parameters on clear cover glass and perpendicular flat target correction applied.

#### 7.4.7 Confidence

For each detected target, the TMF8820/21/28 provides a confidence result. The confidence result is the signal to noise ratio (SNR) of the detected peak in the histogram.

Signal = Peak value in the histogram

Noise = Noise from the device and ambient light = sqrt (baseline level of histogram)

The confidence value is an 8-bit value which supports two encodings:

#### **Linear Encoding**

Selected by setting register bit logarithmic\_confidence = 0.

The values for confidence represents directly SNR and are clipped at 255.

#### Logarithmic Encoding

Selected by setting register bit logarithmic\_confidence = 1.

The values 0...40 represent directly SNR. Values above 40 are exponentially scaled with a growth rate of 5.36%.

Following c-like code fragment converts from the coded value 'confidence' to the actual value 'exp\_conf':

#define CONF\_BREAKPOINT 40

#define EXP\_GROWTH\_RATE 1.053676f

## 7.5 Typical Optical Characteristics

#### 7.5.1 VCSEL

Internal protection ensures no single point of failure will cause the VCSEL to violate the Class 1 Laser Safety.

Laser Safety

Class 1

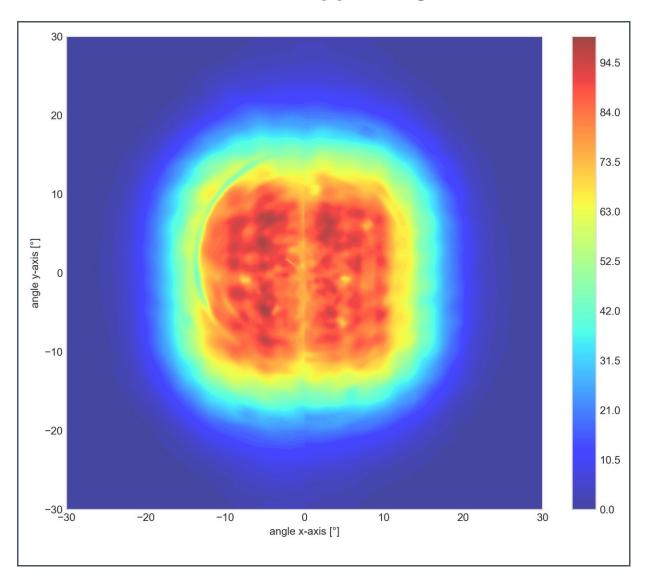

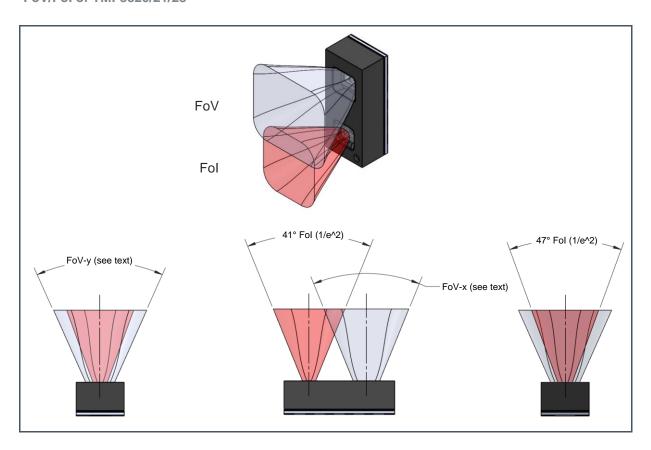

#### 7.5.2 Fol / FoV

VCSEL Field of Illumination (Fol)

```

47x57° (70° diagonal calc.) full width from 5% of maximum up to max.

41x47° (60° diagonal calc.) 1/e^2

```

• 30x32° (43° diagonal calc.) FWHM

#### Information

The smaller value (x/y) for FoI is always into the direction of the SPADs. FWHM ... Full width half maximum

Figure 42: Field of Illumination Shown in Pseudocolors in [%] of Max Range

The sensor field is view (FoV) depends on the chosen spad\_map\_id:

dToF Sensor Field of View (FoV)

41x52° (63° diagonal calc.)

spad\_map\_id=6 or 7

33x32° (45° diagonal calc.)

spad\_map\_id=1

see Figure 30 and Figure 31 – fully customizable FoV.

Figure 43: FoV/FoI of TMF8820/21/28

#### 7.5.3 Optical Filter Characteristics

The on-chip optical filter blocks most of the ambient light and improves the performance especially with sunlight. It is possible to add another optical filter on top to even further improve sunlight performance.

• FWHM 92 nm

Passband Center Wavelength 940 nm (filter only)

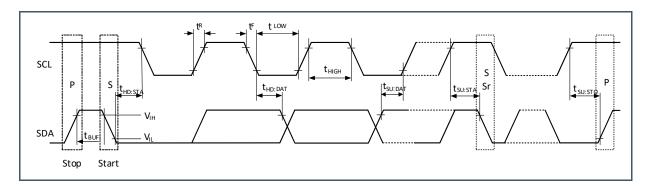

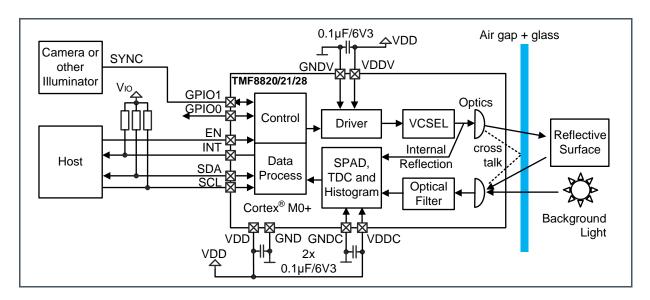

### 7.6 I<sup>2</sup>C Interface

The TMF8820/21/28 is controlled by an I2C bus, one interrupt pin and two GPIO pins.

Additionally see ams OSRAM device driver and/or application note TMF882X\_Host\_Driver\_Communication\_\*.pdf for a detailed explanation of the I<sup>2</sup>C communication itself.

The device uses I<sup>2</sup>C serial communication protocol for communication. The device supports 7-bit chip addressing (default: 0x41) and standard, fast mode and fast mode plus modes. Read and Write

transactions comply with the standard set by Philips (now NXP). For a complete description of the I<sup>2</sup>C protocol, please review the NXP I<sup>2</sup>C design specification.

Figure 44: I<sup>2</sup>C Timings

The TMF8820/21/28 support following I<sup>2</sup>C operating modes:

• Standard mode – up to 100 kBit/s

Fast-mode – up to 400 kBit/s

Fast-mode-plus – up to 1 MBit/s

Figure 45: I<sup>2</sup>C Symbol Definition

| Symbol  | Definition                                                            | RW     | Note               |

|---------|-----------------------------------------------------------------------|--------|--------------------|

| S       | Start condition after stop                                            | R      | 1-bit              |

| Sr      | Repeated start (start condition end without preceding stop condition) | R      | 1-bit              |

| ADR     | Slave address 7 bits = default 0x41                                   | R      | Slave address      |

| WA      | Word address                                                          | R      | 8-bit              |

| A       | Acknowledge                                                           | W      | 1-bit              |

| N       | No Acknowledge                                                        | R      | 1-bit              |

| Data    | Data/write                                                            | R or W | 8-bit              |

| Data(n) | Data/read                                                             | W      | 8-bit              |

| Р       | Stop condition                                                        | R      | 1-bit              |

| WA++    | Slave increment word address                                          | R      | During acknowledge |

Internal to the device, an 8-bit buffer stores the register address location of the byte to read or write. This buffer auto-increments upon each byte transfer and is retained between transaction events (i.e. valid even after the master issues a P (Stop condition) and the I<sup>2</sup>C bus is released). During consecutive Read transactions, the future/repeated I<sup>2</sup>C Read transaction may omit the memory address byte normally following the chip address byte; the buffer retains the last register address +1.

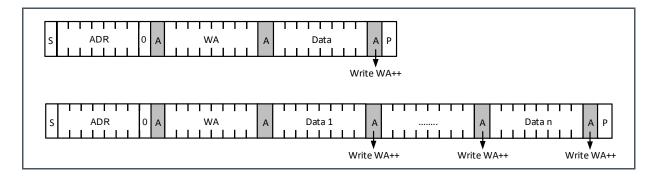

A Write transaction consists of a S, ADR, 0 (R/W flag), WA, Data (n), and P. Following each byte (9th clock pulse) the slave places an A or NA (ACK/NACK) on the bus. If NACK is transmitted by the slave, the master may issue a P.

Figure 46:

Byte Write and Page Write Commands

A Read transaction consists of a S, ADR, 0 (R/W flag), WA, Sr, ADR, 1 (R/W flag), Data(n) and P. Following all but the final byte the master places an A (ACK) on the bus (9<sup>th</sup> clock pulse). Termination of the Read transaction is indicated by a N (NACK) being placed on the bus by the master, followed by STOP.

Figure 47:

Random Read and Sequential Read Command (example shows 2 bytes)

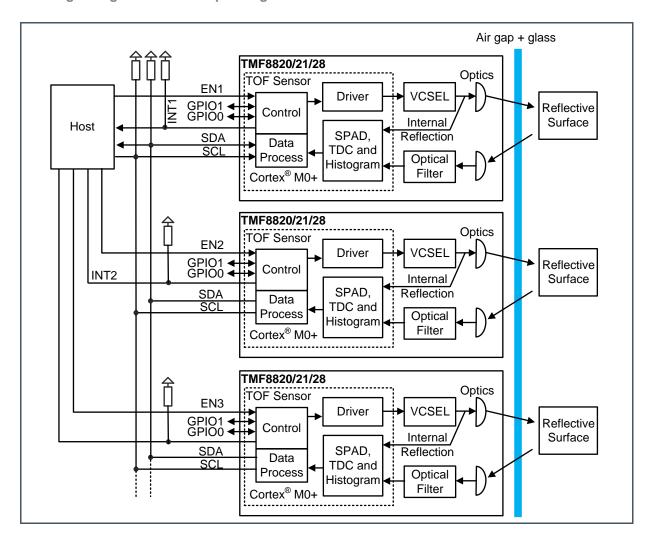

The default I<sup>2</sup>C address is 0x41. The address can be changed after power-up. Use the enable pin to enable only one device at a time to provide unique device addresses – see section 9.1.1.

The device is I<sup>3</sup>C tolerant – therefore it can coexist with I<sup>3</sup>C devices on the same bus. TMF8820/21/28 communicates in legacy I<sup>2</sup>C mode of the I<sup>3</sup>C bus.

#### Attention

During standby and standby timed mode, only register 0xE0 (ENABLE) is accessible by the I<sup>2</sup>C interface.

# 8 Register Description

## 8.1 Register Overview

Please note that the  $I^2C$  register table uses pages. Therefore, the content of the registers depends on the page select register app\_id and cid\_rid.

Figure 48: Register Overview

| Addr      | Name                           | <d7></d7>      | <d6></d6>     | <d5></d5>     | <d4></d4> | <d3></d3>     | <d2></d2> | <d1></d1>     | <d0></d0> |

|-----------|--------------------------------|----------------|---------------|---------------|-----------|---------------|-----------|---------------|-----------|

| Any appid | , any cid_rid – Registers alwa | ıys available  | )             |               |           |               |           |               |           |

| 0x00      | APPID                          | appid          |               |               |           |               |           |               |           |

| 0x01      | MINOR                          | minor          |               |               |           |               |           |               |           |

| 0xE0      | ENABLE                         | 0              | cpu_re<br>ady | powerup       | _select   |               |           |               | pon       |

| 0xE1      | INT_STATUS                     | 0              | int7          | int6          | 0         | int4          | 0         | int2          | 0         |

| 0xE2      | INT_ENAB                       | 0              | int7_en<br>ab | int6_en<br>ab | 0         | int4_en<br>ab | 0         | int2_en<br>ab | 0         |

| 0xE3      | ID                             |                |               | 0             | 0         | 1             | 0         | 0             | 0         |

| 0xE4      | REVID                          |                |               |               |           |               | rev_id    |               |           |

| appid=0x0 | 3, any cid_rid - Main Applica  | ion Registe    | rs            |               |           |               |           |               |           |

| 0x02      | PATCH                          | patch          | patch         |               |           |               |           |               |           |

| 0x03      | BUILD_TYPE                     | build          | build         |               |           |               |           |               |           |

| 0x04      | APPLICATION_STATUS             | app_status     |               |               |           |               |           |               |           |

| 0x05      | MEASURE_STATUS                 | measure_status |               |               |           |               |           |               |           |

| 0x06      | ALGORITHM_STATUS               | alg_status     |               |               |           |               |           |               |           |

| 0x07      | CALIBRATION_STATUS             | fc_status      |               |               |           |               |           |               |           |

| 80x0      | CMD_STAT                       | cmd_stat       |               |               |           |               |           |               |           |

| 0x09      | PREV_CMD                       | prev_cmd       |               |               |           |               |           |               |           |

| 0x10      | MODE (TMF8828 ONLY)            | mode           |               |               |           |               |           |               |           |

| 0x0A      | LIVE_BEAT                      | live_beat      |               |               |           |               |           |               |           |